研究人员将CMOS与随机纳米磁体相结合开发节能计算机

东北大学和加州大学圣巴巴拉分校的研究人员推出了概率计算机原型。该原型可采用近期技术制造,将互补金属氧化物半导体(CMOS)电路与有限数量的随机纳米磁体相结合,创建异构概率计算机。

开发能够有效执行人工智能和机器学习中常用的概率算法的计算机是科学家长期以来一直寻求克服的挑战。这项工作中概述的方法为解决这个问题提供了一种有前途且可行的解决方案,研究人员确认其卓越的计算性能和能源效率超越了当前的CMOS 技术。

这一突破的详细信息发表在2024 年 3 月 27 日的《自然通讯》杂志上。

最近的人工智能和机器学习对社会产生了变革性的影响。在此类技术中,概率算法用于解决固有不确定性或精确解决方案在计算上不可行的问题。这些操作遵循CMOS电路内的特定指令,但有时软件(指令)和硬件(电路)的协同工作方式存在不一致,从而导致结果的差异。

随着人工智能和机器学习的作用不断扩大,人们强烈需要一种新的计算范式来协调这种不匹配,实现更高的复杂性,同时显着降低能耗。

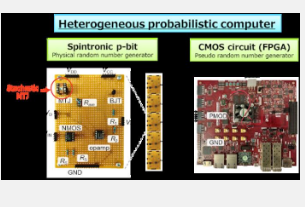

在这项研究中,东北大学的研究生 Keito Kobayashi 和 Shunsuke Fukami 教授,以及加州大学圣塔芭芭拉分校的 Kerem Camsari 博士及其同事,开发了一种近期异构版本的概率计算机,专为执行概率计算而设计。算法和简易制造[图。 1b]。

Fukami 指出:“我们构建的原型表明,通过在确定性 CMOS 电路中驱动伪随机数生成器,并使用有限数量的随机纳米磁体生成的物理随机数,可以实现出色的计算性能。” “具体来说,具有随机磁隧道结(s-MTJ)的有限数量的概率位(p位)应该可以通过近期的集成技术来制造。”

研究人员还澄清,自旋电子概率计算机的最终形式主要由 s-MTJ 组成[图 1]。 1c],在运行概率算法时,与当前的 CMOS 电路相比,面积将减少四个数量级,能耗将减少三个数量级。

最终,Fukami 和同事的原型解决了当前人工智能和机器学习的确定性 CMOS 电路的局限性。 Fukami 补充道:“我们预计未来的研究和开发将会取得进展,从而使具有卓越计算性能和节能能力的创新计算硬件在社会中得到应用。”

免责声明:本文由用户上传,与本网站立场无关。财经信息仅供读者参考,并不构成投资建议。投资者据此操作,风险自担。 如有侵权请联系删除!

-

2025年6月20日,——在世界文化遗产地河南洛阳的光影流转之间,2025年新浪微博旅游之夜盛大举行。作为国内首个...浏览全文>>

-

2025年6月20日,——在世界文化遗产地河南洛阳的光影流转之间,2025年新浪微博旅游之夜盛大举行。作为国内首个...浏览全文>>

-

QQ多米试驾线下预约活动为了让更多用户感受QQ多米的独特魅力,我们特别推出了线下试驾预约活动。这不仅是一次...浏览全文>>

-

阜阳长安启源A07以其卓越的性能和豪华配置吸引了众多消费者的目光。作为一款定位高端市场的新能源车型,长安启...浏览全文>>

-

【安徽淮南大众CC新车报价2025款大公开】大众CC作为一款兼具运动感与豪华质感的轿跑车型,一直深受消费者喜爱...浏览全文>>

-

2025款长安猎手K50在安徽淮南地区的最新价格已新鲜出炉,为准备购车的朋友带来全面解析。这款车型以其高性价比...浏览全文>>

-

在安徽滁州购买长安猎手K50时,了解其落地价和省钱技巧至关重要。长安猎手K50是一款实用性强的皮卡车型,适合...浏览全文>>

-

途锐新能源是大众旗下的一款高端插电混动SUV,目前在安徽阜阳地区有售。其官方指导价约为58万元起,但实际成交...浏览全文>>

-

2025款大众CC作为一款兼具运动与豪华的中型轿车,备受关注。目前市场指导价大约在25万至35万元之间,具体价格...浏览全文>>

-

2024款探岳X作为一款备受关注的中型SUV,在市场上以其时尚的设计和出色的性能吸引了众多消费者。根据最新市场...浏览全文>>

- QQ多米试驾线下预约

- 安徽滁州长安猎手K50落地价,买车省钱秘籍

- 淮南大众CC新款价格2025款多少钱?买车攻略一网打尽

- 瑞虎8 PRO试驾,畅享豪华驾乘,体验卓越性能

- 安徽阜阳长安启源A05多少钱 2025款落地价,换代前的购车良机,不容错过

- 保时捷Macan试驾的流程是什么

- 安徽淮南大众ID.3多少钱?购车攻略在此

- 阜阳揽巡落地价,豪华配置超值价来袭

- 安徽池州威然 2024新款价格与配置的完美平衡

- 奇瑞瑞虎9试驾,新手必知的详细步骤

- QQ多米价格,换代前的购车良机,不容错过

- 池州迈腾GTE新款价格2022款多少钱?选车秘籍与优惠全公开

- 岚图追光多少钱 2024款落地价走势,近一个月最低售价25.28万起,性价比凸显

- 天津滨海威然 2024新款价格,最低售价28.98万起,入手正当时

- 蚌埠途昂新款价格2025款多少钱?购车必看

- 坦克400预约试驾全攻略

- 天津滨海ID.7 VIZZION价格,各配置车型售价全揭晓,性价比之王

- 安庆帕萨特最新价格2025款,最低售价12.35万起,入手正当时

- 亳州宝来新款价格2025款多少钱?选车指南与落地价全解析

- 生活家PHEV 2025新款价格,最低售价63.98万起现在该入手吗?